ALU

arithmetic and logic unit 算术逻辑单元,简称ALU,是计算机的数学大脑,也就是计算机里负责运算的组件,比如把两个数相加。基本其他的组件都用到了ALU,它有两个 单元 一个算术单元,一个逻辑单元

算术单元

算术单元,它主要负责计算机里的所有数字操作,比如加减法,自增自减等。 接下来,使用最简单的加法电路,即两个bit相加,bit是0或者1,来看看它是怎么设计与运行的。

半加器

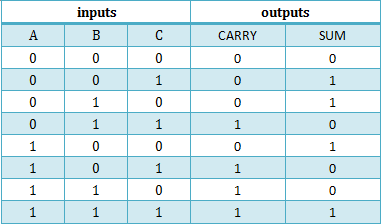

首先有两个输入,A和B,一个输出,即A和B的和,这里三个数A,B,输出,都是单个bit(0或1)。那么输入只有四种可能:

- 0+0=0

- 0+1=1

- 1+0=1

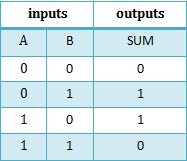

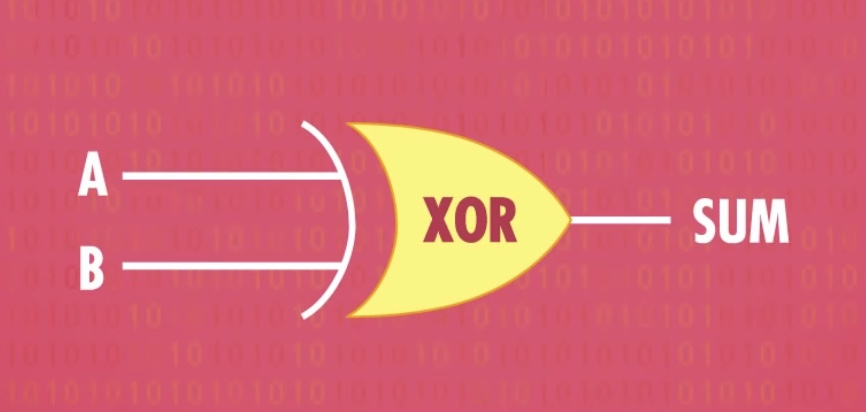

上面这三种的输入和输出,与XOR(异或)门的逻辑是一样的,所以可以用XOR门作为一位加法器,但是第四种组合:1+1 = 2是个特例,但在二进制里没有2,因此1+1的结果是0,1进到下一位。真值表和XOR门与下图所示:

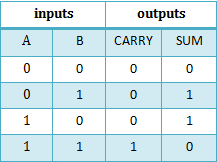

由这两个逻辑门组合而成的组件,就是大名鼎鼎的 半加器 ! 即两个输入 A 和 B 都是 1 位 ,两个输出 "总和" 与 "进位",没有进位输入的加法器电路。

全加器

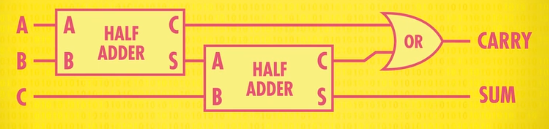

由于半加器没有进位输入,因此想要处理超过1+1的运算,就需要用到 全加器,半加器输出了进位,因此在计算下一列的时候,还有之后的每一列,我们需要将 三个位 加在一起,而不在是两个。

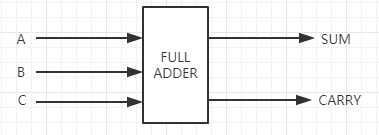

因此全加器有三个输入,A,B,C(都是1个bit),所以最大的可能就是1+1+1,总和1,进位1,因此也需要两条输出线,“总和”和“进位”

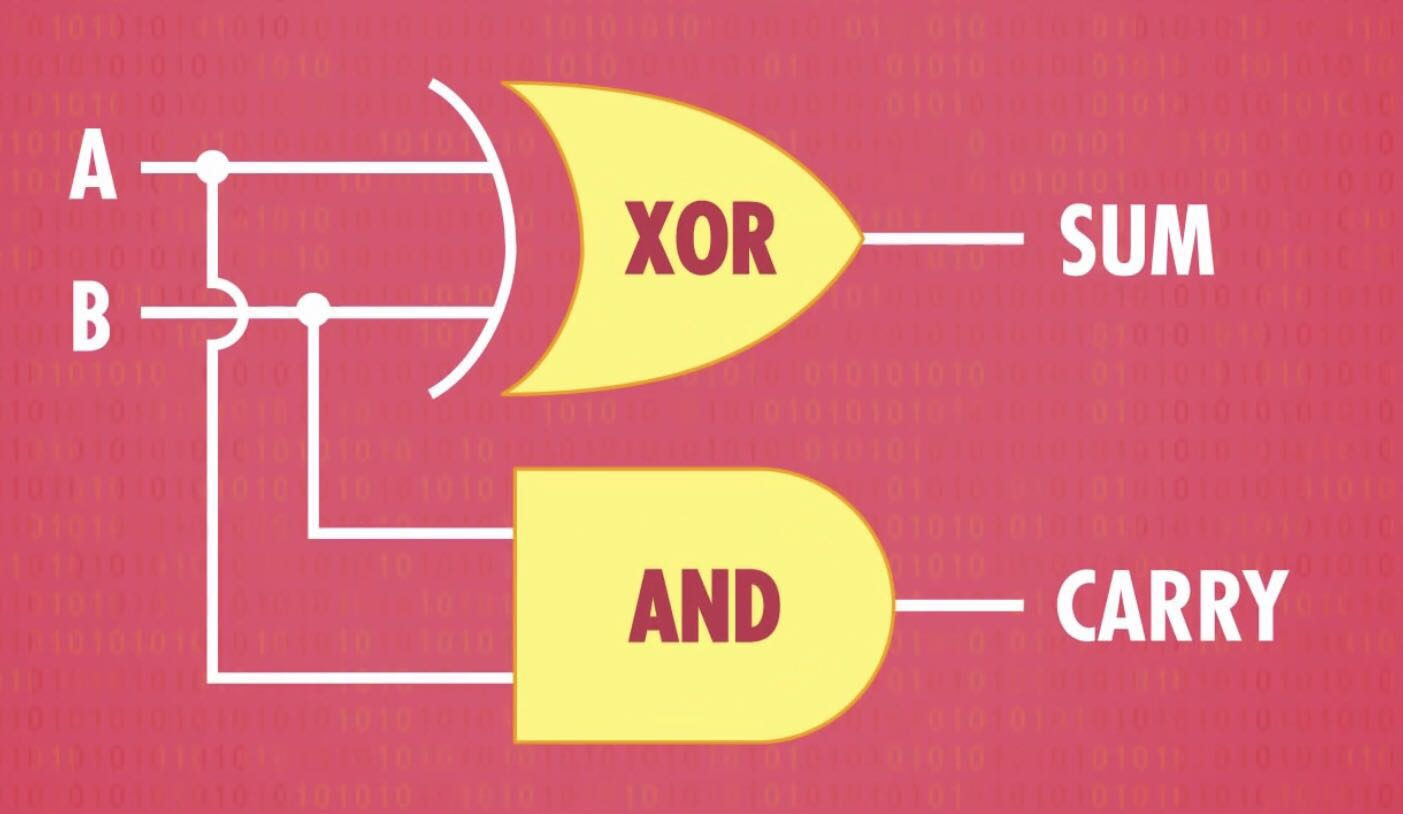

可以使用半加器,做全加器:

先用半加器将A和B相加,然后将C输入到第二个半加器,最后用一个 OR 门检查进位是不是 true。 这样全加器就使用了,来看看真值表和图示:

这就是大名鼎鼎的 全加器 ,它会把三个输入A,B,C加起来,输出“总和”和“进位”。

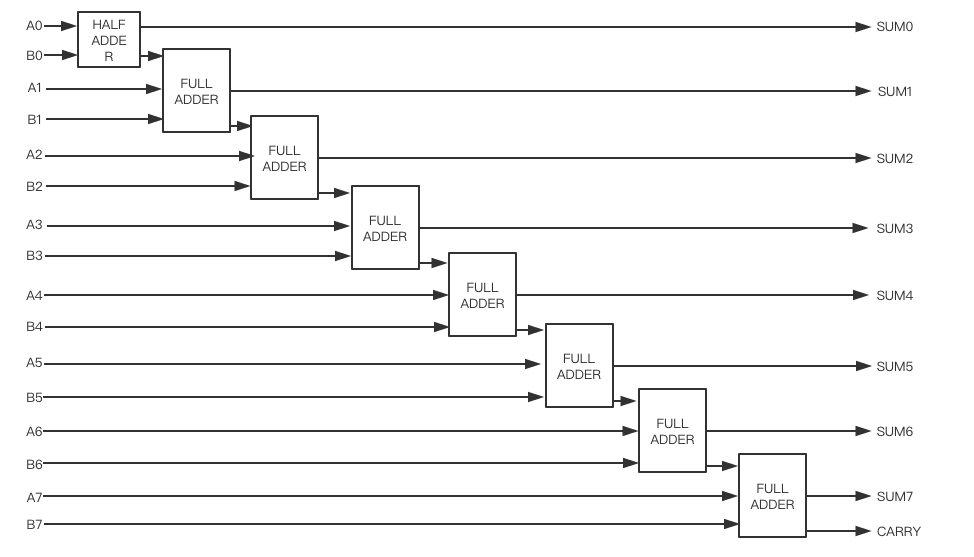

1、先从A和B的第一位开始,称为A0和B0,由于是第一次相加,不用处理任何进位,直接使用 半加器 相加,输出叫sum0;

2、现在相加A1和B1,因为A0和B0的结果有可能进位,所以使用 全加器,除了A1和B1,还要连上进位,输出为sum1;

3、把上一步得到的进位输入到 下一个全加器,处理A2和B2

4、以此类推,处理完8个bit。

如下图所示:

溢出

如果第9位有进位,代表2个数字的和,超过了8个bit,这被称为“溢出(overfloe)”。最著名的就是“吃豆人”的关卡数,因为是使用8个bit记录关卡数的,因此最大值为255,当玩家进入256关的时候,就会发生溢出,导致游戏界面出现乱码。想要避免溢出,可以加更多的全加器,可以操作16或者32个bit的数字,让溢出更难发生,但代价是更多的逻辑门和更长的时间

各种ALU的不同

简单的ALU是没有专门的电路来处理乘法和除法,而是用多次加法来实现乘法,比如12X5,这和将12加5次是一样的,所以要5次ALU操作来实现这个乘法,虽然比较慢(相对而言),但是胜在简单。

比较先进的ALU,比如计算机和手机中,有专门做乘法的部分,乘法电路比加法复杂,但只是需要更多的逻辑门进行组装。

逻辑单元

逻辑单元是执行各种逻辑操作的,比如AND,OR,NOT等操作,也能做简单的数值测试,比如一个数字是不是负数。

总结

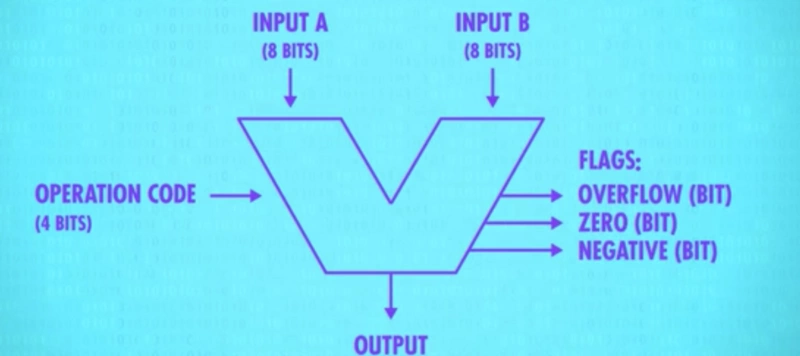

在工程上,工程师们使用大“V”来表示ALU。来看一下8-bit ALU的输入与输出:

- 两个输入:A和B,都是8 bit;

- 操作码: 用4位操作码告诉ALU执行什么操作,比如加法减法,“1000”可能代表加法,“1100”代表减法等;

- 输出结果:一个8 bit

- 标志位:同时也会输出一堆标志(flags),标志是1 bit,代表特定的状态。一般有overflow(溢出),zero(零值),negative(负值)。 例如:如果想知道A 是否小于 B,可以用 ALU 来算 A 减B,看负标志是否为 true,如果是 true,我们就知道 A 小于 B。

Thanks!